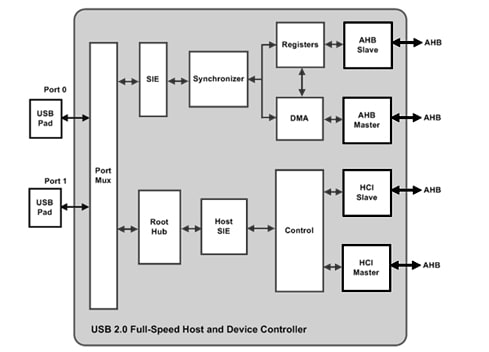

Archimago's Musings: MEASUREMENTS: Computer USB port noise, USB hubs and the 8kHz PHY Microframe Packet Noise

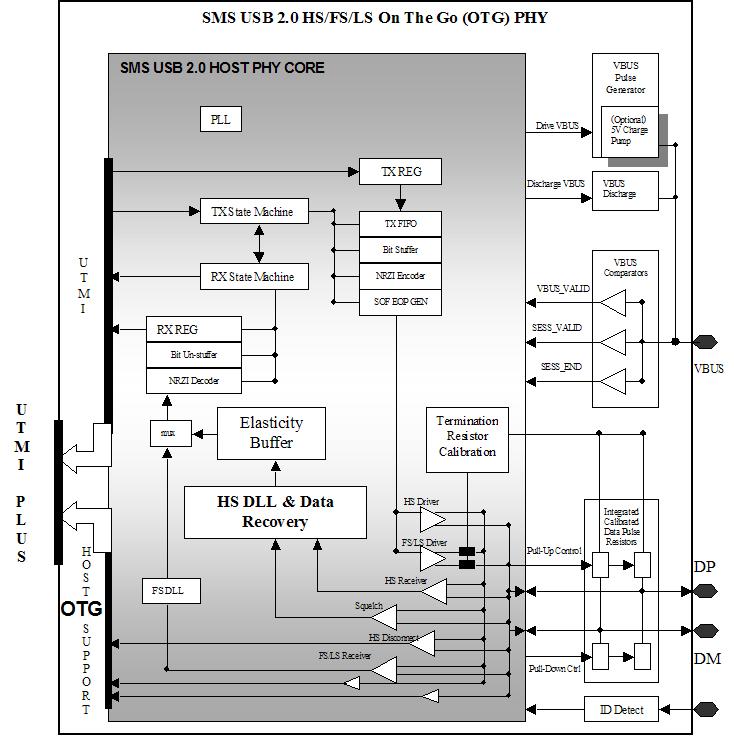

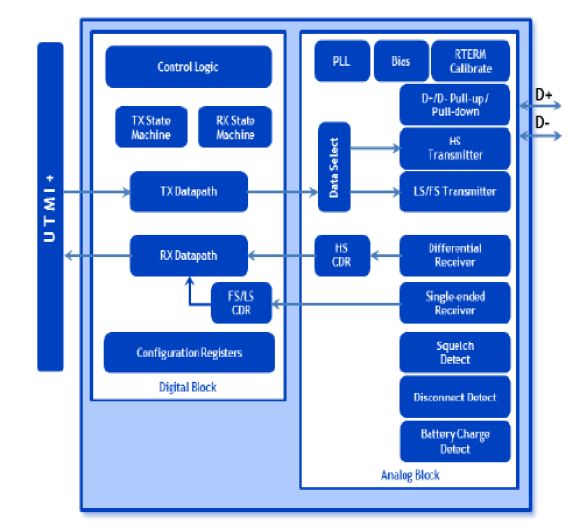

USB 2.0 PHY IP Core Device Host OTG Hub in TSMC, 28HPC, 40LP /LL, UMC, 40LP, 28HPC, SMIC 14SF, SF, 55LL, 40LL - T2M-IP

USB3300 USB High Speed PHY Board ULPI Interface features the USB3300 MIC2075 1BM onboard|Integrated Circuits| - AliExpress

![USB3300 Transceiver: Features, Pinout, and Datasheet [Video&FAQ] USB3300 Transceiver: Features, Pinout, and Datasheet [Video&FAQ]](https://res.utmel.com/Images/UEditor/72083c43-5731-4f70-b870-d0c7fd2bebce.jpg)